And in somewhat related news, the HDL is being re-targeted to an older FPGA from the mid 90s (Xilinx XC3000A series) which I have several dozen of. Not a major overhaul but some things will need split up. I’ll probably just tear all the functional units out of the core and slap them on a 16(writeback)+16(instruction)-bit bus.

Reason being, due to component shortages I’m completely unable to source any more of the configuration devices for the Altera Cyclone III.

Yep, just the little SOIC-8 flash memory, that they vendor-locked to Intel branded EPCSxx chips. It’ll take a few of them to fit the entire design but I’m actually surprised how easy these are to work with.

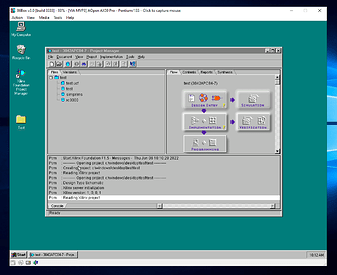

Welcome back, Windows 95. The last supported OS for Xilinx Foundation 1.5i (the last IDE for the XC3000 series), and the only one I’ve been able to get it running on.

Currently emulated on an 86Box Pentium II system, but it’s miserable and so I’ve got a good old Intel 486 Overdrive that’s about to become the new HDL development platform.

TL;DR: New FPGAs are expensive and currently nonexistent, so I’m going back to 1995.