Thanks for the comments about the new BIOS/BMC packages.

you said you updated to a new board, which board was that?

Sorry, I meant I updated BIOS and BMC on a just-out-of-the-box board, as opposed to one that was already in service. It’s the same Rev 1.02A ROMED8-2T that’s been shipping for the last couple years.

On the leftmost cpu socket, what ECC RDIMM are that have heat spreaders on them?

I added them myself mostly for looks although they actually did lower temps by a few degrees(was worried they might have the opposite effect because of lack of airflow between dimms) i haven’t had to time to do the other socket yet.

OK, thanks for the clarification. I was just wondering if I had somehow missed some manufacturer that was making RDIMMS with consumer class heat spreaders.

Do you guys know if Milan-X as a P variant is planned? Would love to see how it performs in 3D particle simulations.

Is new bios supporting both Milan and Milan-x?

Hello everyone ! Just dropping by to tell you I’m planning a ThreadRipper Pro build to replace my workstation. After having failed to find any EPYC board that supports ACPI S4 I have accepted that I’m going to have to buy something of a “gamer” motherboard.

As you might expect, my EPYC server is still peachy. Never anything to complain about, here.

Good luck on your next project.

I have bumped up my compute capacity by upgrading to new 64C/128T cpus on my two workstations. Moving from 24C/48T systems.

I have a 7V12 Rome cpu on the EPYCD8 host and a 7713 Milan cpu on the ROMED8-2T host.

Now the older generation Rome host is faster than the Milan host which is a change I wasn’t expecting. Simply faster clocks on the 7V12.

Following up on this, I took a closer look at ROMED8-2T BIOS 3.20 → 3.40:

- Advanced

- new: Network Stack Configuration, contains options to enable/disable/configure UEFI network stack, both IPv4 and IPV6

- new: Tls Auth Configuration, allows enrolling and removing server CA certs - I assume this is related to the UEFI networking and probably some remote boot options, but not entirely sure

- CPU Configuration

- new: Node 0 Information, contains CPU info like family, microcode revision, etc

- Chipset Configuration

- new: Onboard VGA, enable/disable

- new: AMD PCIE Hotplug, enable/disable for each slot and the OCuLink ports

- changed: PCIE link width and speed is now grouped in submenus, and M.2 slot link speed configuration is added (Gen4/3/2/1)

- Storage Configuration

- new: SATA Hot Plug, a single enable/disable so presumably for all controllers/ports

- removed: PCIE/NVME info display, this section is now SATA only. There’s still a separate menu for NVME info, but it’s not linked to specific slot/port like this one was, and I don’t see another source for this data.

- Server Mgmt

- changed: BMC out of Band Access toggle is replaced with Bonding configuration

I wasn’t thorough with the AMD CBS and PBS sections, but I did note that under NBIO → SMU there’s now an EDC Control option. This is the third SoC performance limiter along with cTDP and Package Power.

In other news, they’ve pulled BMC 1.24 from the download section, it’s back to 1.19 again. Meanwhile the new ROMED8-2T/BCM is apparently on BMC 1.25 and BIOS 3.50. I wonder if they’re compatible…

That doesn’t seem right? What benchmark/workload is that under and what clocks do each boost to?

The 7V12 boosts to 3.30Ghz.

The 7713 boosts to 3.76Ghz

But under my actual BOINC workload the 7V12 can hold all-core load clocks at ~2.90Ghz and the 7713 can only manage all-core load clocks at ~2.54Ghz with the identical BOINC loads. Both cpus set for Power determinism and 240W cTDP and PPT settings. So the 7V12 has better workload throughput now.

Prior to the upgrades, the Milan cpu always beat the Rome cpu in throughput simply because of the better clocks under BOINC loads. Both hosts are set up identically except for the motherboard platforms. The Rome cpus occupy a Asrock Rack EPYCD8 and the Milan cpus occupy a Asrock Rack ROMED8-2T.

The prior 7402P could maintain all-core loads locked permanently to 3.30Ghz on my workload.

But the 7443P could manage ~3.60Ghz all-core loads on my workload. So it was the prior better performer.

Interesting, both that the 7v12 can hold 2.9 at 240w but also did not realize the 7713 was capped that low on all core, makes me want to test my 7742 at 240w.

Keith, I noticed a similar discrepancy in my workloads (mostly rendering, mostly Embree accelerated) moving from a 7742 ES to a final stepping 7713P. Even at 240W cTDP, the 7713P was 1-5% slower than my previous 225W 7742 ES, but this is expected for a couple reasons:

-

Milan doubled the fabric clock to be 1:1 with DRAM speed (3200 MHz unless specified otherwise by the user); it previously operated at half speed up to 1467 MHz. This results in the Milan IOD using a significantly higher portion of package power compared to Rome, lowering the amount of power available to cores.

-

Milan unified the L3 cache per CCD, meaning that L3 bandwidth is effectively halved. Milan’s L3 now serves 8 cores instead of Rome’s 4, and bandwidth was not increased with Milan. This especially hurts parallel workloads that do not benefit from a larger unified cache.

In regard to the later comment on the 7713 being capped, there is no literal cap on all-core frequency, only power. Disabling 4 cores per CCD in the BIOS allows the chip to run the remaining 32 cores well in excess of 3 GHz, because the cores are no longer starved for power. The real solution would be a higher cTDP to mitigate the impact of Milan’s power hungry IOD, but 240 is the maximum on 7713 for market segmentation reasons.

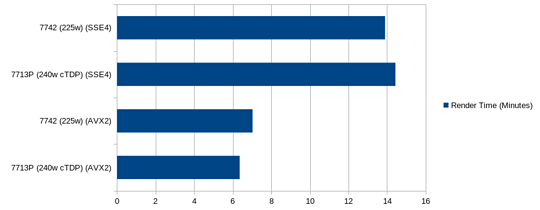

Another mitigation for some workloads is to move your code from SSE to AVX. I see identical clocks of ~2.65 GHz on 7713P when I specify vector width 4 (SSE) and vector width 8 (AVX2) for Embree, yet render times are 40%+ lower with the denser AVX2 code path.

Of course, Rome also supports AVX2, but I see a slight performance uplift over 225w Rome with 240w Milan:

For your processors which are both at 240w, it would probably be a wash.

Thanks so much for your post @rrubberr.

It explains much in regard to what I am seeing. The power being used by the IOD starving the cores of available headroom makes sense.

And my workload is exactly as you described. Multiple single, independent core processes that do not share any common cache data.

The only solution will be to move to a higher TDP processor that would be able to maintain higher clocks. But I need to amortize the cost of this upgrade for a year before considering another upgrade.

I have just upgraded to Bios 3.5 and USB section is empty now

I haven’t tried 3.50 yet, but if it’s like 3.40, it will only show up when you have the Compatibility Support Module enabled (Boot section). The only entry will be enable/disable for “Legacy USB Support”.

Which processors weren’t reporting the correct number of cores that the 3.50 update fixes?

is there a way to update BMC inside bios or usb stick? I am not able to connect to it here in my new office we have local network I add the mac address of the BMC NIC and it pulls an IP but I can’t log in maybe a network restriction? Is there a way to connect a network cable to one of the other two network cards and setup somehow a local network so I can access the BMC. Always struggle with this ![]()

in the BIOS, you cant update BMC, but you can reset BMC to default settings.