So I’m looking at my next X299 board and I’m eyeing the Gigabyte X299 Designare EX.

Seems like the perfect board but there’s one oddity that I find extremely odd:

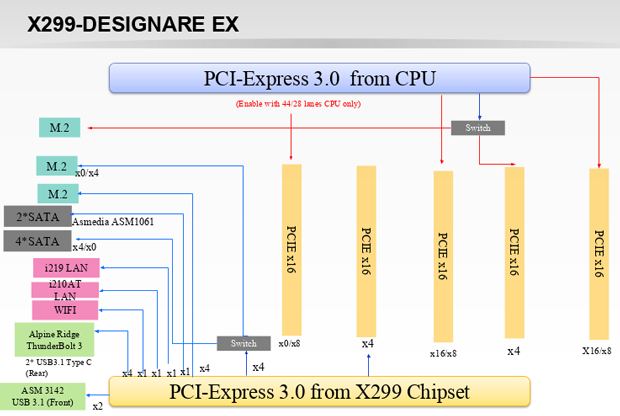

The 3 GPU config for the CPU PCI-E lanes is x8/x16/x8…

However, the X299 Aorus Gaming 7 Pro is the same board minus the Thunderbolt controller, but has the full x16/x16/x8…

All reviews online suggest the Thunderbolt controller on the mobo goes to the chipset, but if a fully populated board drops the first slot to x8, something weird is happening with the lane switching. If the same board design CAN support x16/x16/x8, what’s the limitation? Board design? Lane switching?

The recent Cascade Lake-X updates to the Designare allowed bifurcation of the PCI-E lane partitioning so that each x4 partition can be separated:

So then why do the lane switchers still cripple the top slot when fully populated? Were the materials not updated for Cascade Lake-X, or was the board designed that way?

I would like an lstopo on this board, and a trace analysis of it to see where the traces for that Thunderbolt controller are actually going. If the Thunderbolt controller is indeed sharing traces with the lanes for the top slot, that is honestly bad design to provide a feature, and I would literally switch over to the Aorus Gaming 7 Pro for that reason, since the lanes actually matter.

There’s no detailed block diagram for both boards so I need people who own these boards to check the traces.

If the x4 lanes from the Thunderbolt controller are going to the chipset, they should stay isolated rather than share traces. If traces are shared, it’s bad design.

I’m grasping at straws trying to figure this out… No use contacting their PR/Support since I need to actually speak to a engineer for the board to figure out why this is happening.