First off, a big thanks to reddit user CyclingChimp and his workaround post on reddit. Please head over there for his reasoning on this workaround. This post merely serve to make more people aware and some setup examples.

As for performance gains, I saw no performance gains in either Cinebench R15(probably same story as R20), 3D Mark Firestrike, PCMark10 and Farcry 5. All fall within 1 - 2% error margin. However Aida64 do show a big jump in L3 cache read/write/copy performance. My conclusion is that this workaround allows users to pin whatever cpu core they want, with minor performance increase or decrease.

Implementation example with 6 vCpu on 24 core 3960X

...

<vcpu placement="static" current="12">48</vcpu>

<vcpus>

<vcpu id="0" enabled="yes" hotpluggable="no"/>

<vcpu id="1" enabled="yes" hotpluggable="yes"/>

<vcpu id="2" enabled="yes" hotpluggable="yes"/>

<vcpu id="3" enabled="yes" hotpluggable="yes"/>

<vcpu id="4" enabled="yes" hotpluggable="yes"/>

<vcpu id="5" enabled="yes" hotpluggable="yes"/>

<vcpu id="6" enabled="no" hotpluggable="yes"/>

<vcpu id="7" enabled="no" hotpluggable="yes"/>

<vcpu id="8" enabled="yes" hotpluggable="yes"/>

<vcpu id="9" enabled="yes" hotpluggable="yes"/>

<vcpu id="10" enabled="yes" hotpluggable="yes"/>

<vcpu id="11" enabled="yes" hotpluggable="yes"/>

<vcpu id="12" enabled="yes" hotpluggable="yes"/>

<vcpu id="13" enabled="yes" hotpluggable="yes"/>

<vcpu id="14" enabled="no" hotpluggable="yes"/>

<vcpu id="15" enabled="no" hotpluggable="yes"/>

<vcpu id="16" enabled="no" hotpluggable="yes"/>

<vcpu id="17" enabled="no" hotpluggable="yes"/>

<vcpu id="18" enabled="no" hotpluggable="yes"/>

<vcpu id="19" enabled="no" hotpluggable="yes"/>

<vcpu id="20" enabled="no" hotpluggable="yes"/>

<vcpu id="21" enabled="no" hotpluggable="yes"/>

<vcpu id="22" enabled="no" hotpluggable="yes"/>

<vcpu id="23" enabled="no" hotpluggable="yes"/>

<vcpu id="24" enabled="no" hotpluggable="yes"/>

<vcpu id="25" enabled="no" hotpluggable="yes"/>

<vcpu id="26" enabled="no" hotpluggable="yes"/>

<vcpu id="27" enabled="no" hotpluggable="yes"/>

<vcpu id="28" enabled="no" hotpluggable="yes"/>

<vcpu id="29" enabled="no" hotpluggable="yes"/>

<vcpu id="30" enabled="no" hotpluggable="yes"/>

<vcpu id="31" enabled="no" hotpluggable="yes"/>

<vcpu id="32" enabled="no" hotpluggable="yes"/>

<vcpu id="33" enabled="no" hotpluggable="yes"/>

<vcpu id="34" enabled="no" hotpluggable="yes"/>

<vcpu id="35" enabled="no" hotpluggable="yes"/>

<vcpu id="36" enabled="no" hotpluggable="yes"/>

<vcpu id="37" enabled="no" hotpluggable="yes"/>

<vcpu id="38" enabled="no" hotpluggable="yes"/>

<vcpu id="39" enabled="no" hotpluggable="yes"/>

<vcpu id="40" enabled="no" hotpluggable="yes"/>

<vcpu id="41" enabled="no" hotpluggable="yes"/>

<vcpu id="42" enabled="no" hotpluggable="yes"/>

<vcpu id="43" enabled="no" hotpluggable="yes"/>

<vcpu id="44" enabled="no" hotpluggable="yes"/>

<vcpu id="45" enabled="no" hotpluggable="yes"/>

<vcpu id="46" enabled="no" hotpluggable="yes"/>

<vcpu id="47" enabled="no" hotpluggable="yes"/>

</vcpus>

<cputune>

<vcpupin vcpu="0" cpuset="18"/>

<vcpupin vcpu="1" cpuset="42"/>

<vcpupin vcpu="2" cpuset="19"/>

<vcpupin vcpu="3" cpuset="43"/>

<vcpupin vcpu="4" cpuset="20"/>

<vcpupin vcpu="5" cpuset="44"/>

<vcpupin vcpu="8" cpuset="6"/>

<vcpupin vcpu="9" cpuset="30"/>

<vcpupin vcpu="10" cpuset="7"/>

<vcpupin vcpu="11" cpuset="31"/>

<vcpupin vcpu="12" cpuset="8"/>

<vcpupin vcpu="13" cpuset="32"/>

<emulatorpin cpuset="6-8,18-20,30-32,42-44"/>

</cputune>

...

<topology sockets="1" cores="24" threads="2"/>

...

Implementation example with 6 vCpu on 6 core cpu

...

<vcpu placement="static" >12</vcpu>

<vcpus>

<vcpu id="0" enabled="yes" hotpluggable="no"/>

<vcpu id="1" enabled="yes" hotpluggable="yes"/>

<vcpu id="2" enabled="yes" hotpluggable="yes"/>

<vcpu id="3" enabled="yes" hotpluggable="yes"/>

<vcpu id="4" enabled="yes" hotpluggable="yes"/>

<vcpu id="5" enabled="yes" hotpluggable="yes"/>

<vcpu id="6" enabled="no" hotpluggable="yes"/>

<vcpu id="7" enabled="no" hotpluggable="yes"/>

<vcpu id="8" enabled="yes" hotpluggable="yes"/>

<vcpu id="9" enabled="yes" hotpluggable="yes"/>

<vcpu id="10" enabled="yes" hotpluggable="yes"/>

<vcpu id="11" enabled="yes" hotpluggable="yes"/>

<vcpu id="12" enabled="yes" hotpluggable="yes"/>

<vcpu id="13" enabled="yes" hotpluggable="yes"/>

<vcpu id="14" enabled="no" hotpluggable="yes"/>

<vcpu id="15" enabled="no" hotpluggable="yes"/>

</vcpus>

<cputune>

<vcpupin vcpu="0" cpuset="#example"/>

<vcpupin vcpu="1" cpuset="#example"/>

<vcpupin vcpu="2" cpuset="#example"/>

<vcpupin vcpu="3" cpuset="#example"/>

<vcpupin vcpu="4" cpuset="#example"/>

<vcpupin vcpu="5" cpuset="#example"/>

<vcpupin vcpu="8" cpuset="#example"/>

<vcpupin vcpu="9" cpuset="#example"/>

<vcpupin vcpu="10" cpuset="#example"/>

<vcpupin vcpu="11" cpuset="#example"/>

<vcpupin vcpu="12" cpuset="#example"/>

<vcpupin vcpu="13" cpuset="#example"/>

<emulatorpin cpuset="#example"/>

</cputune>

...

<topology sockets="1" cores="6" threads="2"/>

...

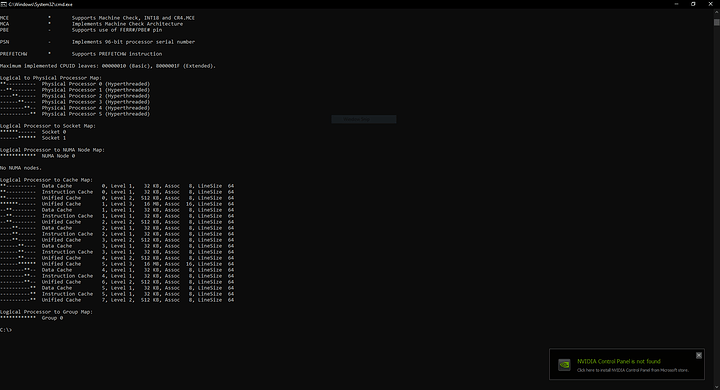

Workaround:

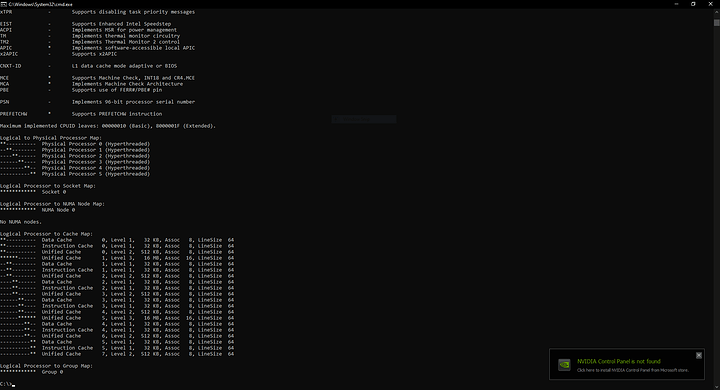

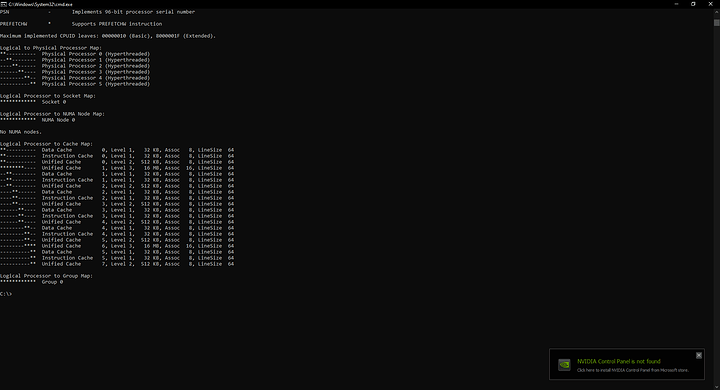

Before workaround:

My old workaround: