What Torpcoms has been looking at

Talos II news

POWER9 chips, modules

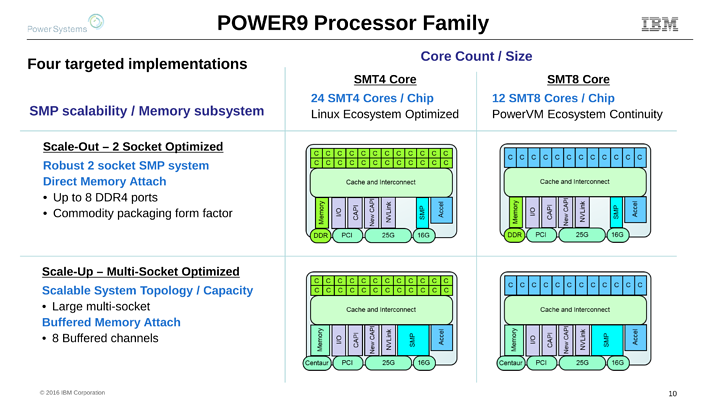

I think I finally figured out what is going on with the different POWER9 processor chips and sockets/modules. There are three chips planned:

|

PowerNV |

PowerVM |

| Scale Out |

Nimbus |

??? |

| Scale Up |

|

Cumulus |

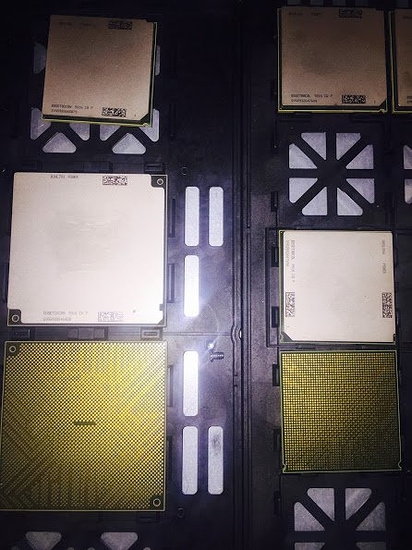

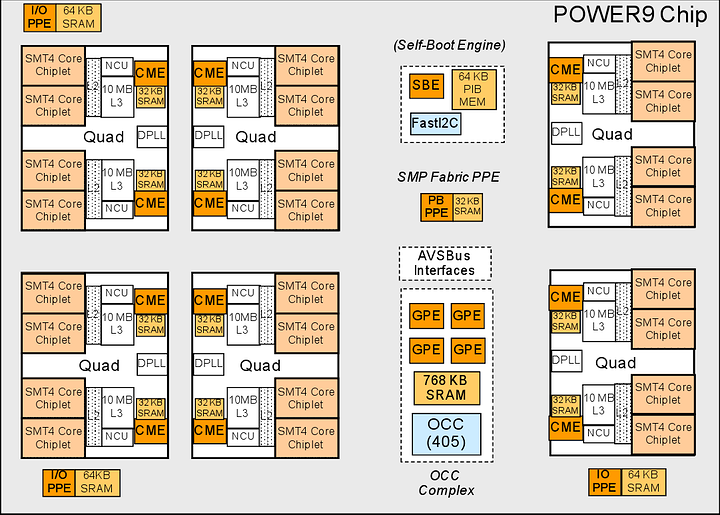

Nimbus chips - are packaged as Sforza, Monza, or LaGrange modules. They are made with 24 SMT4 cores on the die. Sforza modules are 50 mm × 50 mm, smaller than the Monza and LaGrange modules which are 68,5 mm × 68,5 mm. I don’t know if LaGrange and Monza sockets are physically the same or not.

Cumulus chips - are planned for use in NUMA machines with many sockets. These are made with 12 SMT8 cores on the die, and use centaur-buffered RAM to address much more memory than Nimbus chips. I have seen nothing about what modules will be available.

??? chips - There were plans for Scale Out chips for PowerVM use, but I have seen no mention in the news as to what these chips might be called. These would be SMT8 chips meant for 2-core systems using direct-attached RAM.

Scale Up PowerNV chips (SMT4 with buffered RAM) are a theoretical design possibility, but IBM does not expect to actually make these.

Chips vs Modules

The modules of a chip such as Sforza, Monza, LaGrange, are different packages for the same silicon that expose different IO.

Chip types explained in more detail

There is a matrix you will usually see in POWER9 presentations (and articles using those slides) about chips being made for both the “Linux Ecosystem” or the “PowerVM Ecosystem” and both “Scale Up” or “Scale Out” machines.

Linux Ecosystem Community - as far as I can tell in this context, is synonymous with OpenPOWER; OpenPOWER systems run as PowerNV (not-virtualised) meaning that software runs bare metal, without the PowerVM hypervisor. In my table I use PowerNV for this category; since Linux can run on PowerVM, saying Linux ecosystem is more confusing.

PowerVM Community - refers to systems running software on top of IBM’s PowerVM hypervisor. This is the pre-OpenPOWER way of running software on POWER machines (random history: originally the flag indicating that the hypervisor is running was undocumented, and no one even knew there was a hypervisor in their system).

Scale Up - refers to machines with many sockets. These can be components of systems like IBM’s E880, where an entire cabinet with multiple racks functions as one machine. In the matrix, you will see that there is more SMP connectivity so that all processors (16 sockets is the maximum from what i can tell) can talk to each other.

Scale Out - refers to machines designed for two sockets. These can be stand alone boxes, and have directly attached memory in POWER9, while in POWER8 all machines used Centaur buffered memory.

SMT8 vs SMT4 - Power9 cores are designed out of “execution slices”. Compared to an SMT8 core, an SMT4 core has half the number of these slices. This is why POWER9 chips are either 12 or 24 core, both have the same number of slices. Pairs of SMT4 cores also share cache, since that pair would be a single core on an SMT8 chip.

I have been trying to figure this out for a while, looking through articles from IT Jungle, Next Platform, asking around on reddit’s /r/OpenPOWER, watching presentations on OpenPOWER (I mention some of them in the Talos thread). The POWER9 presentations recorded by the AIX Virtual User Group are especially helpful, though their site is an AJAX monstrosity, so here is a direct link to where the recordings+slides are. I also watch the Raptor Engineering GNU Social account, and sometimes their and Raptor Computing’s Twitter accounts for Talos-specific news. If I know something, you can probably find more detail in one of those places.