Starting a casual dev blog here.

Don’t expect super in-depth updates or for things to be in any kind of intelligent order, but I’m gonna chronicle the interesting bits that I’ve been working on here instead of dumping it in The Lounge to be buried.

I’ll toss links to sections here as I put them up as a kinda table of contents.

For the people reading this who have no idea what the title’s talking about:

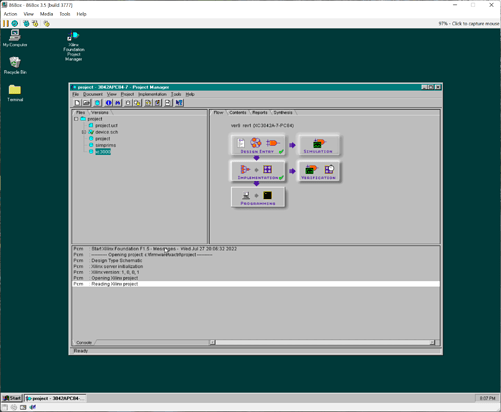

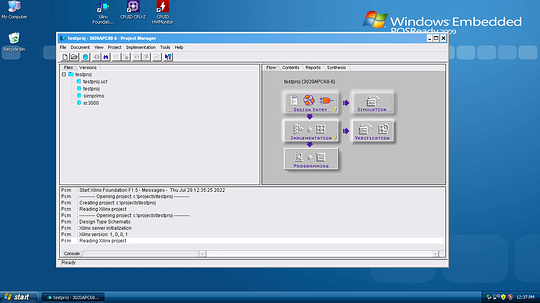

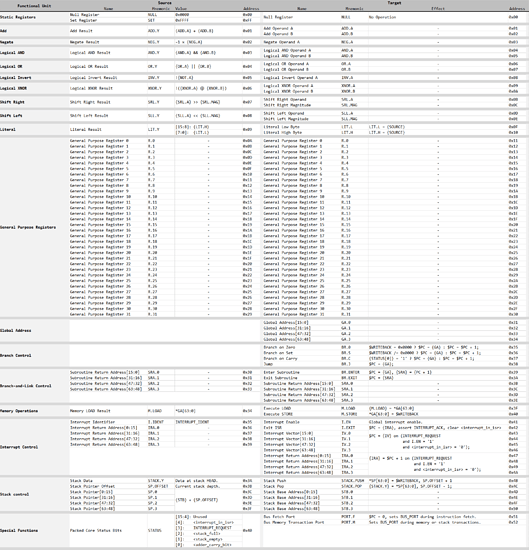

This is a continuation of the Devember 2021 project. My task was to create an entirely new CPU core from the ground up, built on a transport-triggered architecture and implemented on an FPGA. If this sounds interesting, I’ll be putting up more detailed explanations in this thread as I improve and re-implement the Devember proof-of-concept.

The ultimate goal here is to have the entire system built and assembled for Devember 2022 (…it’s happening, right? ![]() ), where my next challenge will be to write as assembler and maybe even start on porting a C compiler to the architecture.

), where my next challenge will be to write as assembler and maybe even start on porting a C compiler to the architecture.