What is Ram / Memory Refresh?

Dynamic Random Access Memory, DRAM for short as is used in computers is a form of volatile memory and therefore is prone to loosing it's information when unpowered.

What you may not know however is exactly how DRAM is powered in the first place and how does it store information electrically?

DRAM is effectively in general terms best described as a very large bank of capacitors arranged in rows and columns. Each capacitor is known as a cell.

Depending on the charge retained in the cell we are able to determine if that cell is storing a 1 or a 0. A bit if you will.

Unfortunately capacitors have this annoying property of loosing their charge over time due to various thermodynamic and other effects, these get worse the smaller or warmer the capacitors cells become

Sidenote: Cooling your RAM down to very low temperatures is a great trick to retaining the charge in the memory cells for longer.

Now due to this problem of capacitors in DRAM loosing their charge we need to top up this charge from time to time in order to avoid loosing the state of the bit in that cell.

This is what we call Memory Refresh.

Memory refresh is the process of periodically reading information from an area of computer memory and immediately rewriting the read information to the same area without modification, for the purpose of preserving the information.

This process is carried out periodically by the memory circuitry all the time in the background.

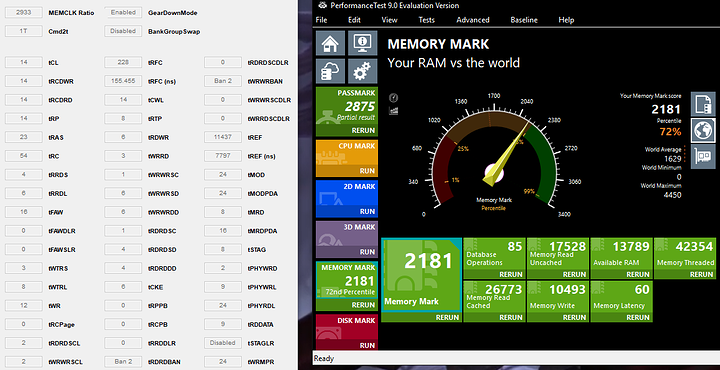

The interval or period of how often this occurs is known as the tREF in most BIOS menus.

The time it takes for it to complete a Refresh is what we refer to as the Refresh Cycle.

Commonly called tRFC in the BIOS menu's you may have seen.

Both these values are usually measured in number of clock cycles.

| Refresh Period |

| Refresh Cycle | Access | Access | Access | Access | Access |

<--|---------------------|--------|--------|--------|--------|--------|-->On the above chart we can see a simplified excerpt of RAM chips operation. The Refresh period is effectively a waiting interval that counts down cycles until another Refresh Cycle is needed. Before then returning to normal access operation.

Keep this chart in mind for latter.

The unfortunate aspect is that while a refresh is occurring the memory is not available for normal read and write (access) operations. This is known as refresh overhead, since it takes away useable time from the computer being able to access the RAM.

Some Introductory Math

Let's for example take the following two example values.

I Recently used these for calculating & tuning refresh overhead on the Ryzen platform.

Here are the two examples we shall use:

3200Mhz with a 0.3125 nS(nanoSecond) period and

3333Mhz with a 0.30003 nS(nanoSecon) period.

Now you may say, wait a minute. How is 3200 Mhz 0.3125 ns?

Well you see due to various mathematical reasons involving the definition of a circle, the period of any frequency is defined as

Period = 1/Frequency

Hence:

3200Mhz = 1/3.2 x 10-9 = 0.3125 x 10-9

So, just as an example lets see what happens in 10 nano Seconds:

(10 / 0.30003) = ~33 clock cycles in 10Ns at 3333Mhz

(10 / 0.3125) = 32 Clock cycles at 3200Mhz

CAS Latencies

For example let's take a stick of DDR4 3200Mhz Gskill RAM with CAS latencies of 14.

We previously calculated how much time a single cycle takes.

For our 3200Mhz example the period of a single cycle was 0.3125nS

0.3125 * 14 = 4.375ns

So 14 Cycles (CAS) will take 4.375 nanoseconds.

Which is clearly faster than CL18 RAM at 3200Mhz

0.3125 * 18 = 5.625ns

But What is CAS?

CAS - less commonly referred to as Column Address Strobe in general terms is the delay time between the moment a memory controller tells the memory to access a particular memory column on a RAM module, and the moment the data from the given array location is available on the memory module's output pins.

SIdenote: This means that any data we ask for is output with a very specific time delay, no sooner and no later. It is also why if you set your RAM latencies lower than what the RAM circuit can respond, the data will be returned later than our computer is expecting it and read it incorrectly. Thus not being stable or even posting at all.

In simple terms you may equate this to Clock cycles per Instruction, it's the effectively the smallest unit of work a memory chip cam perform, similar to processor Instructions per Clock.

So a CAS 14 RAM chip effectively performs 1 action in 14Clock cycles, or rather as we previously calculate, 4.375ns.

Let's extrapolate this over time and see how for a full second the CL14 RAM chip can get a lot more done than a CL18 RAM chip.

3.125 x 109 / 14 = 223214285.714 accesses/second

3.125 x 109/ 18 = 173611111.111 accesses/second

You can now see how the factors you often use such as CAS Latencies are actually factors of time and can be used to calculate how efficient any particular DRAM chip is.

And the shorter the units of time required for a task, the fast the task can complete.

Calculating Memory Refresh Overhead

We can calculate refresh overhead using the following formula:

overhead = time required for refresh (ms) / refresh interval (ms)

For a start we are going to assume the following values:

tREF: 13'000 Cycles

tRFC: 270 CyclesAs well as the two clock frequencies from before

3200Mhz or 3.125 x 109 Hz

3333Mhz or 3.333 x 109 Hz

So lets calculate our refresh overhead as follows:

Don't forget to multiply values by 2x, this is DDR (Double Data Rate) Memory after all

(270(tRFC)*0.30003) * 2(DDR) / 1000 (ms)

----------------------

(13000(tREF) * 0.30003) *2 / 1000 (ms)

= 0.162 / 7.8

= 0.0207713076923

x by 100 to get percentage overhead

= 2.07713076923%

~ 2.08%

--------Which means that roughly 2.1% of the memory's on-time is taken by refresh cycles where it is inaccessible.

Now lets calculate the same in reverse for a tREF of 155nS at 3200MHz:

(155ns / 0.3125(period)) / 2(DDR) = 248 cycles.So now we have our tRFC at 3200Mhz

But we still need our tREF value for 3200Mhz. Since less clock cycles elapse tREF now becomes smaller since. But on average we should still refresh the memory every 7800ns.

Sidenote: Increasing the memory voltage can allow you to increase the refresh period since the cells may retain more of a charge for longer.

This means that you will have to refresh your memory less often and can instead access it during that time.

There are even more interesting details here but those are beyond the scope of this post.

Let's calculate how many clock cycles elapse at 3200Mhz in 7800ns.

(7800ns / 2(DDR)) / 0.3125(period) = 12480 cycles

So to calculate our overhead

(248(tRFC)*0.3125(period)) * 2(DDR) / 1000 (conv to ms)

--------------------------------------------------------

(12480(tREF) * 0.3125(period)) *2(DDR) / 1000 (conv to ms)

= 0.155 / 7.8

= 0.0198717948718

x by 100 to convert to percent

= 1.98717948718

~ 1.98%So overall there is a difference of only around (2.08 - 1.98 = 0.1%) in overhead between such differently clocked RAM as used in our example.

Overhead here being defined as time for which the RAM is inaccessible during a refresh cycle.

I hope this post has been insightful to you and vote if you want to see more like this in future.

- more

- meh

0voters

Votes are public.