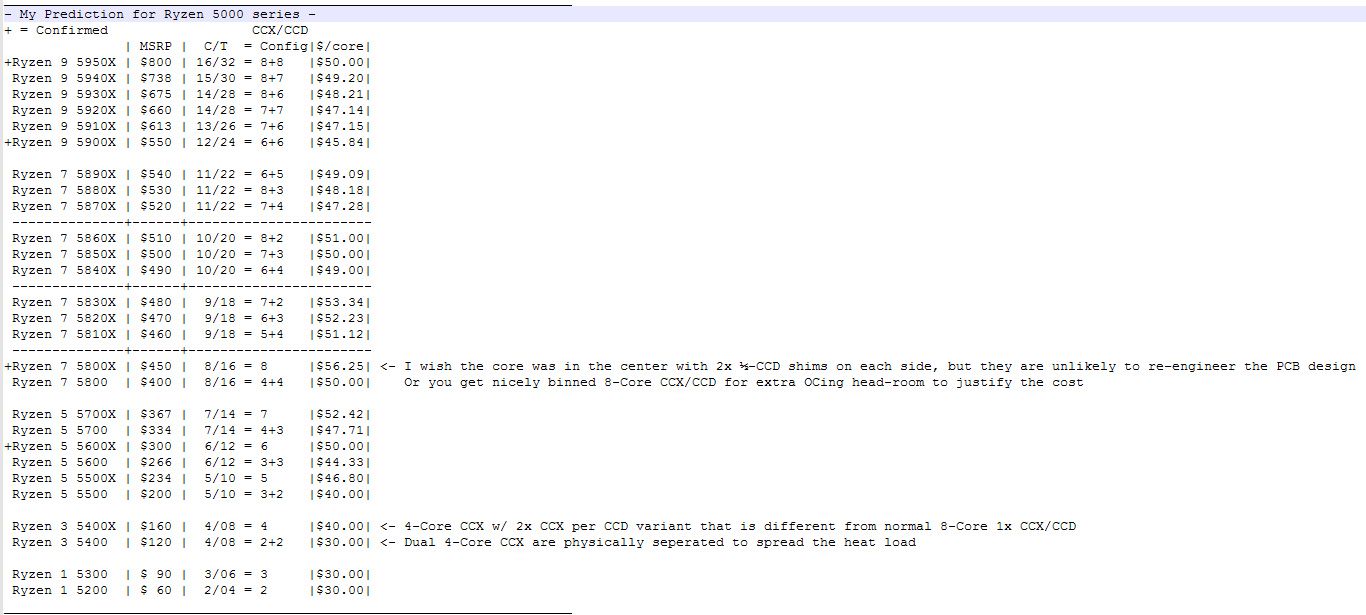

So given the information we know about the existing Ryzen 5000 series CPU product stack, I’m going to try to predict the future with some educated guesses.

Here’s my current forecast / prediction into the future

Take everything I predict with a grain of salt.

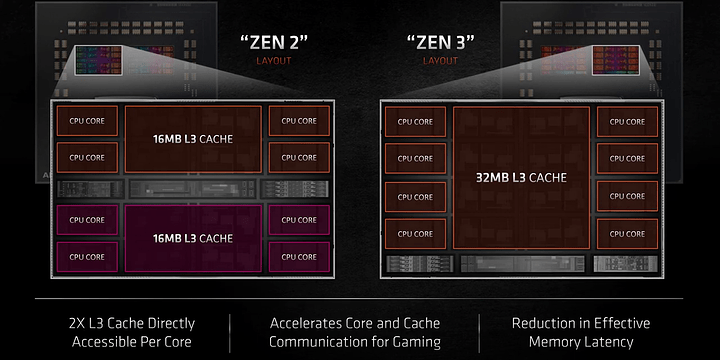

The one thing that strikes me is that Zen 3 will eventually need a 4-Core CCX part to cover their bottom end of the product stack.

Do you think that they’ll just update the existing Zen 2 4-Core CCX die and update it to Zen 3 and leave out 16 MB of L3 cache and call it a day?

I think that’s incredibly plausible since it would require the least amount of work.

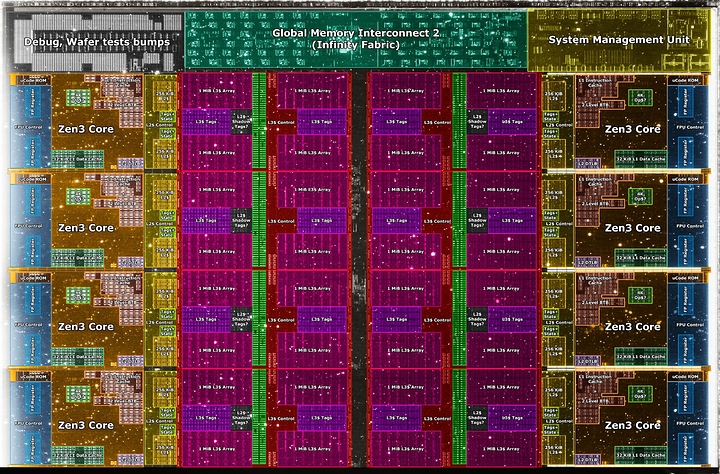

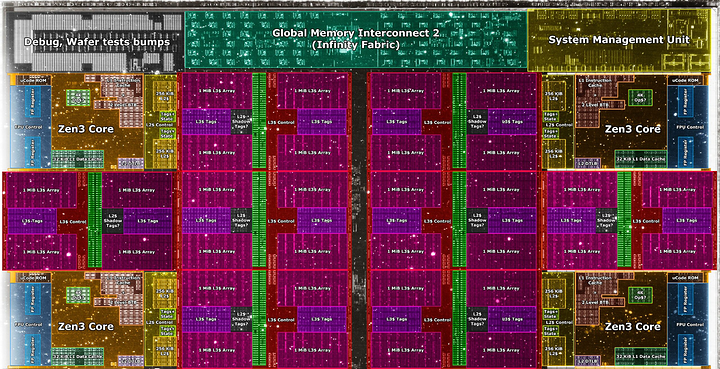

If they were to make a new 4-Core CCX with 32 MB of L3 cache, what would it’s die layout look like?

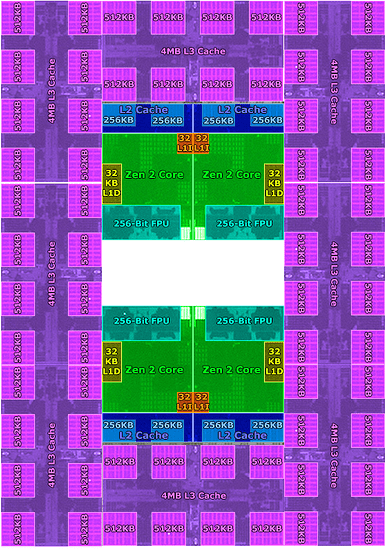

My prediction for what it would look like is this.

That’s a chicken scratch version, there would be a Double Direction Ring Bus linking to each chunk of 512 KiB L3 cluster that can be shared amongst all 4-core CCX’s. The center white area between Cores would be some sort of Infinity Fabric link/Switch that can filter around data between the 4-Cores and the L3 Cache clusters on the RingBus. The advantage to placing the 4 cores right next to each other is latency between the 4 cores should be far less due to distance. The disadvantage is L3 latency will vary depending on how far away data is and how long it will take to propagate to L2 via the Central Switch.

But that’s just me thinking up of a unique solution to a problem that might happen.

Realistically, I think they would update the Zen 2 4-Core CCX and just omit the extra 16 MB of cache and call it a day. Slap those 4-Core CCX into the bottom tiers & mix and match based on binning of defective cores.

That requires the least amount of effort to the existing manufacturing process.

@wendell what do you think about the future of the Ryzen 5000 product stack with the information you know.

Any fun guesses as to what the product stack might look like?

Anybody else want to take a serious stab at guessing the future of Zen 3 Ryzen 5000 product stack?