For the first time ever I will probably be using all slots and all lanes on a motherboard, so I took a look at the board manual.  I know, right

I know, right

Well, I have a hard time understanding how pcie lanes are shared between slots and devices on this board. Here is the link to the user manual:

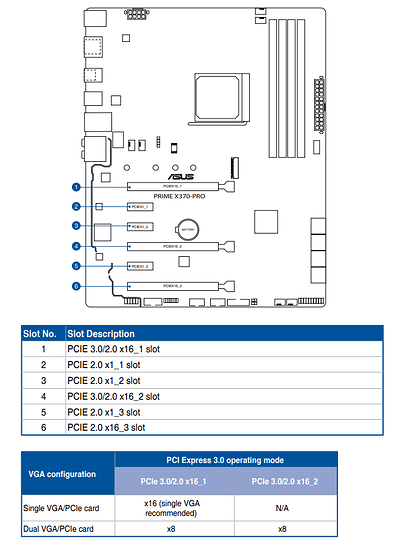

I am looking at page 20 and 21 of the pdf. As far as I understand, on the x370 platform with Ryzen, as soon as I use both slot 1 and 4 (the first two full length slots) these two slots will be running with pcie gen3 x8 right? However, when I look at the bottom table on page 21 the second x16 slot shares bandwidth with the chipset, the M.2 slot and the Asmedia connector (I am guessing sata?). So does this mean the M.2 slot is connected via the chipset and somehow shares bandwidth with the second pcie slot that is usually used for dual gpu setups? This is completely different than on every other board that I have seen.

I just want to arrange my expansion cards in a way that makes most use of the bandwidth without bottlenecking. I don’t use all simultaniously so I am trying to make sense of the pcie lane sharing on this board.

Here is the table I am talking about:

I am an idiot. How did I not read that?

I am an idiot. How did I not read that?