Also this Anandtech article provides evidence that although it’s the same socket, it’s not the same chip/package: http://www.anandtech.com/show/11697/the-amd-ryzen-threadripper-1950x-and-1920x-review/3

The bandwidth numbers that Anandtech are providing are not measuring the same things when comparing Thread ripper to making the article incorrect.

The interconnects that Zen uses are all clocked at actual memory frequency and transfer 32 Bytes/cycle. That is true for Ryzen, Treadripper and Epyc. The Fabric itself is like a backplane and supports an unreported number of GB/s but that number is in excess of 200GB/s. The same interconnects are also used for communication access to PCIe controllers and inter core communication

With 3200MT/s Ram installed, The maximum bandwidth that is available is 51.2GB/s over each interconnect. Threadripper makes use of 2 dual channel memory controllers, one on each of the two dies meaning that the total bandwidth available to all cores to the system memory is 102.4GB/s. Each core can still only access 51GB/s.

For all levels of Zen architecture, CCX modules contain 4 cores each and each CCX has one interconnect to the fabric. Each Die has 2 interconnects to the fabric. Meaning that Thread Ripper has 4 interconnects between the dies for cross dies communication. Each interconnect is 51GB/s each and is the maxumum transfer rate between cores. The total bandwidth is over 200GB/s

An Epyc Chip has 4 dual channel memory controllers. The interconnects are exactly the same at 32 Bytes/cycle also clocked at Ram frequency.

That means an Epyc CPU, with the same speed memory as the TR system has a total available bandwidth to system memory of 204.8Gb/s. Each CCX still only has one interconnect so inter does core to core maximum transfer rates us still limited to 51GB/s but the chips total bandwidth if you add up the total to all ccx modules is 8 x 51GB/s = 408GB/s total on the chip but that number is backplane bandwidth and is really rather academic as useful bandwidth is a limited by the slowest link in the chain.

They are correct that there is tiered performance level models. Switching to other cores on the same CCX takes 40ns, switching to the other CCX takes about 80 and switching to the other die adds another 40ns. Epyc adds an extra tier if it is being used in a dual socket installation where the intersocket traffic adds an extra 100ns on top of the latency cost on a single package.

Anandtech has confused the measurement for the bandwidth of a single interconnect on Epyc with the total bandwidth available to system RAM available to the entire TR package.

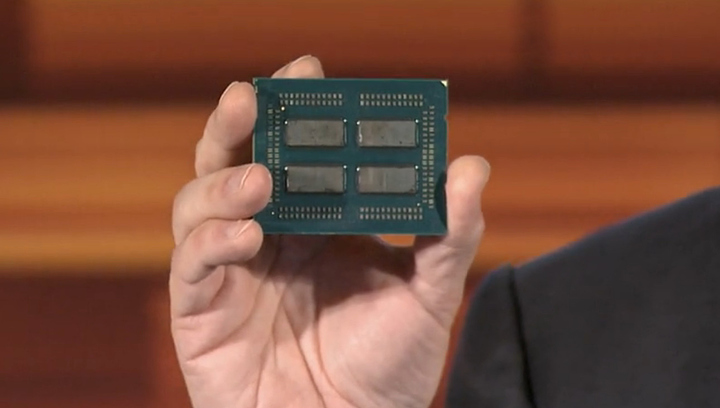

The Epyc Package still has 4 working Dies and TR only has 2 operational dies. Epyc has 8 channel memory, TR only 4 channel memory. Epyc has 128 PCIe lanes, TR only 64. The physical socket itself is the same, the differences are in what is wired up to the socket, making a x399 incompatible with Epyc CPUs

There the same from my little look at it. BUT the Thread ripper substrates are missing the edge area surface mount parts and if have blank dies in place for the missing cores to keep the heat spreader level . Simple Stupid Logic.

Now if the sockets are the same then the question is can you jerry rig them. Well if the MB is only wired up for dual channel memory then sure only that can possibly work.

Will a 32 core epic chip run in a TR MB with dual channel memory and 64 PCI lanes. Well the thing that makes TR a beast is clock speed … +4 Ghz is what a user wants. Hell users want +5Ghz chips and games.

But servers want nothing more than performance VS dollars because speed in Ghz does not matter only how much work can be done because server workloads are pure multithreaded to the max.

Skyrim on EPYC would prolly suck. But be power efficient on the few cores it uses would be ok.

there are 4 dies on a threadripper, all of them contain transistors. The 2 that are unused are not blank silicon. AMD has admitted that the unused dies are faulty and would otherwise have ended up in land fill.

AMD are using binned dies so that they know what is working and what isnt before the manufacturing run on a production line that can manufacture both Epyc and TR packages. Deleting certain surface mounted components that are not needed is trivial given that you already know what you are going to manufacture.

AMD claim that Epyc will not work in a thread ripper socket. I assume the chip checks if the wiring is there at start up. If 1/2 the memory slots are missing it just stops the boot. The physical metal socket is the same hardware.

Gaming issues on epyc will be similar to what they are on TR. If the game is running on a die that does not attach directly to the GPU, the performance will be worse than if you set the CPU affinity to keep everything on the same die.

Look at the top left and bottom right and you can see the pads with no surface mount components

EPYC Delidded bad pic but you can see its fully populated

those components are delete options on TR. The pads to accept the components are still there. I dont think anyone is suggesting that AMD did not know that the production run they were making was specifically for TR or for Epyc model CPUs. What has been said is that they are using the same production line, substrate etc and that Thread ripper is basically an Epyc without some working bits.

They have already said that the dies used have been binned. They need to know that before then make the package.

My point was it would be a EPIC waste of silicon if good dies where on the top left and bottom right of the package tested or not. I dont think AMD is that stupid.

Im totally out of my league here but at step the cores get put on substrates it would not be hard to make every TR have blanks on top left, bottom right. If AMD put actual processors on them to balance the heat spreader I will face palm.

Then again if they plan TR to have more cores than 16 soon. I dont dont know Im puilling lint out of my navel.

If they are binning chips, then the 2 extras can be the failed ones that could be headed for landfill. I dont for a moment think that AMD are destroying fully working Epyc Chips to sell as TR.

I really don’t think that we will see any 32 core Threadripper Chips. The architecture relies on having a PCIE controller and memory controller on the local die. x399 mother boards don’t have the ability to support any more than two dies with quad channel memory. AMD already have a 32 core CPU in epyc. All multi zen chips with the same die and core count will perform pretty much the same. It is always possible that AMD will create an X499 chipset to support epyc chips running as a desktop.