Hello all !

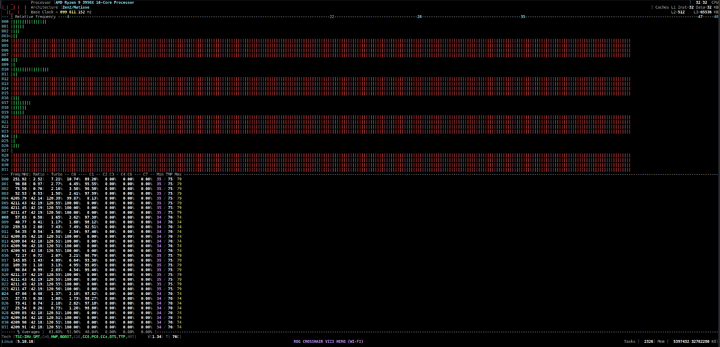

I achieved to set a vm with pci passthrough, I did some optimization with cpu pinning too but in a monitoring app, I only have 1 vcpu at +90% while I am playing.

Specs :

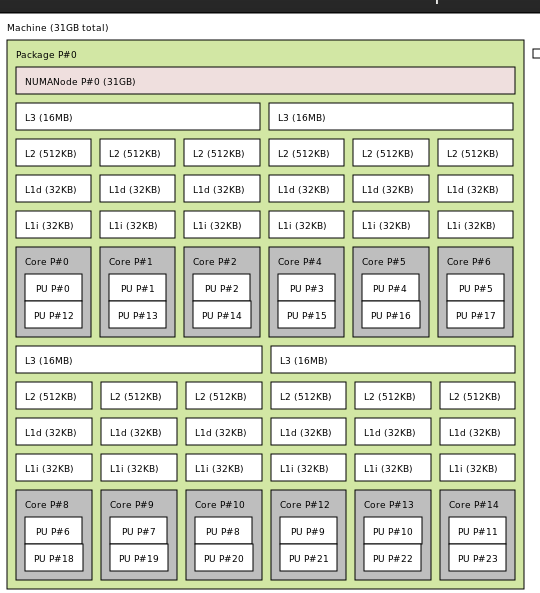

r9 3900x (3cores to host, 9 to guest)

asus x570 e gaming

gt1030 (host)

rtx 3090 fe (guest)

ram 32 GB

ssd nvme 500GB (host)

ssd nvme 500GB (raw disk for guest)

I want to stream/record when I play but it seems the VM is using only 1 vcpu. I tested web navigation and playing at same time but fps dropped significantly.

Is there a way to solve this ? SMT ? a better cpu pinning with threads ?

The xml file (edit : Last xml file used here Performance in a vm - Gaming :

<domain xmlns:qemu="http://libvirt.org/schemas/domain/qemu/1.0" type="kvm">

<name>win10</name>

<uuid>76b97cbc-27a8-49c9-9b4f-8095c2e9673d</uuid>

<metadata>

<libosinfo:libosinfo xmlns:libosinfo="http://libosinfo.org/xmlns/libvirt/domain/1.0">

<libosinfo:os id="http://microsoft.com/win/10"/>

</libosinfo:libosinfo>

</metadata>

<memory unit="KiB">16777216</memory>

<currentMemory unit="KiB">16777216</currentMemory>

<memoryBacking>

<hugepages/>

</memoryBacking>

<vcpu placement="static">16</vcpu>

<cputune>

<vcpupin vcpu="0" cpuset="4"/>

<vcpupin vcpu="1" cpuset="16"/>

<vcpupin vcpu="2" cpuset="5"/>

<vcpupin vcpu="3" cpuset="17"/>

<vcpupin vcpu="4" cpuset="6"/>

<vcpupin vcpu="5" cpuset="18"/>

<vcpupin vcpu="6" cpuset="7"/>

<vcpupin vcpu="7" cpuset="19"/>

<vcpupin vcpu="8" cpuset="8"/>

<vcpupin vcpu="9" cpuset="20"/>

<vcpupin vcpu="10" cpuset="9"/>

<vcpupin vcpu="11" cpuset="21"/>

<vcpupin vcpu="12" cpuset="10"/>

<vcpupin vcpu="13" cpuset="22"/>

<vcpupin vcpu="14" cpuset="11"/>

<vcpupin vcpu="15" cpuset="23"/>

</cputune>

<os>

<type arch="x86_64" machine="pc-q35-4.2">hvm</type>

<loader readonly="yes" type="pflash">/usr/share/edk2/ovmf/OVMF_CODE.fd</loader>

<nvram>/var/lib/libvirt/qemu/nvram/win10_VARS.fd</nvram>

<bootmenu enable="yes"/>

</os>

<features>

<acpi/>

<apic/>

<hyperv>

<relaxed state="on"/>

<vapic state="on"/>

<spinlocks state="on" retries="8191"/>

<vpindex state="on"/>

<synic state="on"/>

<stimer state="on"/>

<vendor_id state="on" value="0123456789ab"/>

<frequencies state="on"/>

</hyperv>

<kvm>

<hidden state="on"/>

</kvm>

<vmport state="off"/>

<ioapic driver="kvm"/>

</features>

<cpu mode="host-passthrough" check="none">

<topology sockets="1" dies="1" cores="8" threads="2"/>

<cache mode="passthrough"/>

<feature policy="require" name="topoext"/>

</cpu>

<clock offset="localtime">

<timer name="rtc" tickpolicy="catchup"/>

<timer name="pit" tickpolicy="delay"/>

<timer name="hpet" present="no"/>

<timer name="hypervclock" present="yes"/>

</clock>

<on_poweroff>destroy</on_poweroff>

<on_reboot>restart</on_reboot>

<on_crash>destroy</on_crash>

<pm>

<suspend-to-mem enabled="no"/>

<suspend-to-disk enabled="no"/>

</pm>

<devices>

<emulator>/usr/bin/qemu-system-x86_64</emulator>

<disk type="file" device="disk">

<driver name="qemu" type="raw" cache="none" io="native" discard="unmap"/>

<source file="/win10/win10.img"/>

<target dev="vda" bus="virtio"/>

<boot order="1"/>

<address type="pci" domain="0x0000" bus="0x04" slot="0x00" function="0x0"/>

</disk>

<disk type="block" device="disk">

<driver name="qemu" type="raw" cache="writeback" io="threads" discard="unmap"/>

<source dev="/dev/disk/by-id/ata-CT2000MX500SSD1_2046E4CA86BD"/>

<target dev="vdb" bus="virtio"/>

<address type="pci" domain="0x0000" bus="0x0b" slot="0x00" function="0x0"/>

</disk>

<disk type="file" device="cdrom">

<driver name="qemu" type="raw"/>

<source file="/home/urameshi/Téléchargements/Win10_20H2_v2_English_x64.iso"/>

<target dev="sdb" bus="sata"/>

<readonly/>

<boot order="2"/>

<address type="drive" controller="0" bus="0" target="0" unit="1"/>

</disk>

<disk type="file" device="cdrom">

<driver name="qemu" type="raw"/>

<source file="/home/urameshi/Téléchargements/virtio-win-0.1.190.iso"/>

<target dev="sdc" bus="sata"/>

<readonly/>

<boot order="3"/>

<address type="drive" controller="0" bus="0" target="0" unit="2"/>

</disk>

<disk type="file" device="cdrom">

<driver name="qemu" type="raw"/>

<source file="/home/urameshi/Téléchargements/virtio-win-0.1.185.iso"/>

<target dev="sdd" bus="sata"/>

<readonly/>

<boot order="4"/>

<address type="drive" controller="0" bus="0" target="0" unit="3"/>

</disk>

<controller type="usb" index="0" model="qemu-xhci" ports="15">

<address type="pci" domain="0x0000" bus="0x02" slot="0x00" function="0x0"/>

</controller>

<controller type="sata" index="0">

<address type="pci" domain="0x0000" bus="0x00" slot="0x1f" function="0x2"/>

</controller>

<controller type="pci" index="0" model="pcie-root"/>

<controller type="pci" index="1" model="pcie-root-port">

<model name="pcie-root-port"/>

<target chassis="1" port="0x10"/>

<address type="pci" domain="0x0000" bus="0x00" slot="0x02" function="0x0" multifunction="on"/>

</controller>

<controller type="pci" index="2" model="pcie-root-port">

<model name="pcie-root-port"/>

<target chassis="2" port="0x11"/>

<address type="pci" domain="0x0000" bus="0x00" slot="0x02" function="0x1"/>

</controller>

<controller type="pci" index="3" model="pcie-root-port">

<model name="pcie-root-port"/>

<target chassis="3" port="0x12"/>

<address type="pci" domain="0x0000" bus="0x00" slot="0x02" function="0x2"/>

</controller>

<controller type="pci" index="4" model="pcie-root-port">

<model name="pcie-root-port"/>

<target chassis="4" port="0x13"/>

<address type="pci" domain="0x0000" bus="0x00" slot="0x02" function="0x3"/>

</controller>

<controller type="pci" index="5" model="pcie-root-port">

<model name="pcie-root-port"/>

<target chassis="5" port="0x14"/>

<address type="pci" domain="0x0000" bus="0x00" slot="0x02" function="0x4"/>

</controller>

<controller type="pci" index="6" model="pcie-root-port">

<model name="pcie-root-port"/>

<target chassis="6" port="0x15"/>

<address type="pci" domain="0x0000" bus="0x00" slot="0x02" function="0x5"/>

</controller>

<controller type="pci" index="7" model="pcie-root-port">

<model name="pcie-root-port"/>

<target chassis="7" port="0x16"/>

<address type="pci" domain="0x0000" bus="0x00" slot="0x02" function="0x6"/>

</controller>

<controller type="pci" index="8" model="pcie-root-port">

<model name="pcie-root-port"/>

<target chassis="8" port="0x17"/>

<address type="pci" domain="0x0000" bus="0x00" slot="0x02" function="0x7"/>

</controller>

<controller type="pci" index="9" model="pcie-root-port">

<model name="pcie-root-port"/>

<target chassis="9" port="0x18"/>

<address type="pci" domain="0x0000" bus="0x00" slot="0x03" function="0x0" multifunction="on"/>

</controller>

<controller type="pci" index="10" model="pcie-root-port">

<model name="pcie-root-port"/>

<target chassis="10" port="0x19"/>

<address type="pci" domain="0x0000" bus="0x00" slot="0x03" function="0x1"/>

</controller>

<controller type="pci" index="11" model="pcie-root-port">

<model name="pcie-root-port"/>

<target chassis="11" port="0x8"/>

<address type="pci" domain="0x0000" bus="0x00" slot="0x01" function="0x0" multifunction="on"/>

</controller>

<controller type="pci" index="12" model="pcie-to-pci-bridge">

<model name="pcie-pci-bridge"/>

<address type="pci" domain="0x0000" bus="0x08" slot="0x00" function="0x0"/>

</controller>

<controller type="pci" index="13" model="pcie-root-port">

<model name="pcie-root-port"/>

<target chassis="13" port="0x9"/>

<address type="pci" domain="0x0000" bus="0x00" slot="0x01" function="0x1"/>

</controller>

<controller type="pci" index="14" model="pcie-root-port">

<model name="pcie-root-port"/>

<target chassis="14" port="0xa"/>

<address type="pci" domain="0x0000" bus="0x00" slot="0x01" function="0x2"/>

</controller>

<controller type="virtio-serial" index="0">

<address type="pci" domain="0x0000" bus="0x03" slot="0x00" function="0x0"/>

</controller>

<controller type="scsi" index="0" model="lsilogic">

<address type="pci" domain="0x0000" bus="0x0c" slot="0x01" function="0x0"/>

</controller>

<interface type="direct">

<mac address="52:54:00:9d:41:3d"/>

<source dev="enp6s0" mode="bridge"/>

<model type="virtio"/>

<link state="up"/>

<address type="pci" domain="0x0000" bus="0x01" slot="0x00" function="0x0"/>

</interface>

<interface type="network">

<mac address="52:54:00:5d:4e:d5"/>

<source network="default"/>

<model type="virtio"/>

<address type="pci" domain="0x0000" bus="0x0e" slot="0x00" function="0x0"/>

</interface>

<input type="tablet" bus="usb">

<address type="usb" bus="0" port="3"/>

</input>

<input type="mouse" bus="virtio">

<address type="pci" domain="0x0000" bus="0x09" slot="0x00" function="0x0"/>

</input>

<input type="keyboard" bus="virtio">

<address type="pci" domain="0x0000" bus="0x0a" slot="0x00" function="0x0"/>

</input>

<input type="mouse" bus="ps2"/>

<input type="keyboard" bus="ps2"/>

<hostdev mode="subsystem" type="pci" managed="yes">

<source>

<address domain="0x0000" bus="0x0b" slot="0x00" function="0x0"/>

</source>

<address type="pci" domain="0x0000" bus="0x05" slot="0x00" function="0x0"/>

</hostdev>

<hostdev mode="subsystem" type="pci" managed="yes">

<source>

<address domain="0x0000" bus="0x0b" slot="0x00" function="0x1"/>

</source>

<address type="pci" domain="0x0000" bus="0x06" slot="0x00" function="0x0"/>

</hostdev>

<hostdev mode="subsystem" type="usb" managed="yes">

<source>

<vendor id="0x1e7d"/>

<product id="0x2cef"/>

</source>

<address type="usb" bus="0" port="2"/>

</hostdev>

<hostdev mode="subsystem" type="pci" managed="yes">

<source>

<address domain="0x0000" bus="0x0e" slot="0x00" function="0x4"/>

</source>

<address type="pci" domain="0x0000" bus="0x0d" slot="0x00" function="0x0"/>

</hostdev>

<redirdev bus="usb" type="spicevmc">

<address type="usb" bus="0" port="4"/>

</redirdev>

<redirdev bus="usb" type="spicevmc">

<address type="usb" bus="0" port="5"/>

</redirdev>

<memballoon model="virtio">

<address type="pci" domain="0x0000" bus="0x07" slot="0x00" function="0x0"/>

</memballoon>

</devices>

<qemu:commandline>

<qemu:arg value="-object"/>

<qemu:arg value="input-linux,id=mouse1,evdev=/dev/input/by-id/usb-ROCCAT_ROCCAT_Kova-event-mouse"/>

<qemu:arg value="-object"/>

<qemu:arg value="input-linux,id=kbd1,evdev=/dev/input/by-id/usb-SINO_WEALTH_USB_KEYBOARD-event-kbd,grab_all=on,repeat=on"/>

</qemu:commandline>

</domain>

Return of lstopo :

Thank you for replying

)

) don’t get me started).

don’t get me started).