Did anybody know/check connections between TR4 socket and DIMM banks on X399?

Maybe they are connect on other pins of TR4?

In this case there is hope for octa-channel for Tr2?

No chance for 8 channel on X399. No 8 channel on TR2.

Both board and chip need to be designed for it.

It can be.

Needed connection between DIMMs bank can be internal thing of TR1, not X399 MB. Why not?

In this case, Tr2 would use these independent connections to handle quad DIMMs.

Did AMD say anything about quad-channel for Tr2?

I seem to remember something in one of the interviews that came out recently.

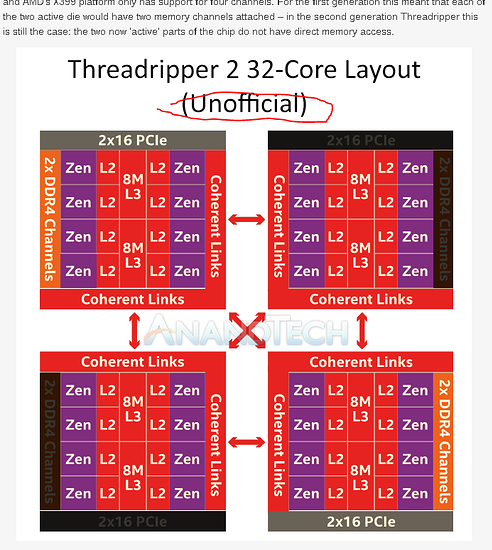

Or it was a chip schematic, basically 4 controllers are fused off

OK, thanks.

Hope dies last. Time will tell.

the tr2 32c will likely have full 8 channel memory.

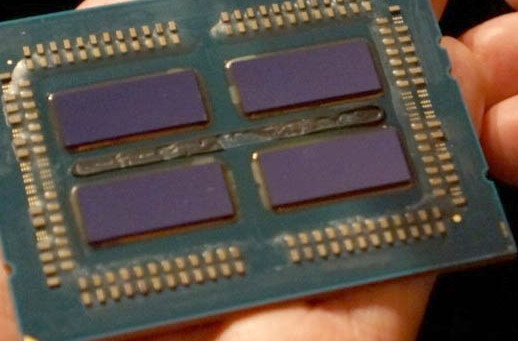

This is TR1 notice, following nodes are just a dummies.

Epyc 32c uses full die, and each 4 cores need their own memory controller and 2 dimms.

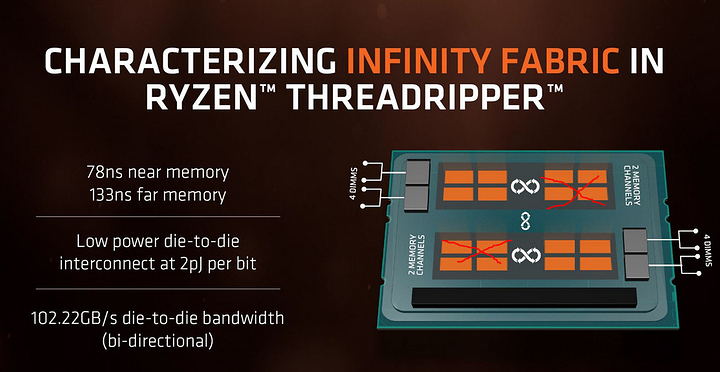

Unless they plan to use infinity fabric - which will result in bad performance while using 16 other cores that don’t have their own memory controller.

The boards are not equipped for octo-channel memory.

From what I gleened TR2 will have a memory bottleneck that is quad channel ! Quad channels is fast still. Intel’s xeon mock up was six channel.

So EPYC with 8 channel is still king so to speak. Come next year at 7nm even more epic.

Computex as always teases with no details. Im sure Wendel and every tech site will put 32 cores vs 16 through video rendering and other professional workloads. To test its worth.

And of course game benchmark 32 core CPU’s. Because

AMD has already confirmed that it’s quad channel memory and two of the dies will not have direct memory access.

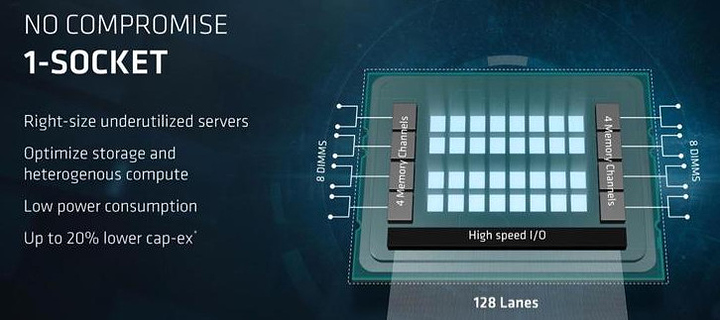

The primary difference between threadripper and epyc is the memory channels and PCIe due to either the chipset/socket or actual package not having all of the parts for those features to reduce costs.

So TR2 will not have those features; not on X399 and i very much doubt on X499 (or whatever the successor is) either.

There is already an existing 8 channel, 128 PCIe version of Threadripper. It’s called EPYC. If you need those features, you buy EPYC instead.

Also… this will be even worse for (current) games than threadripper 1 if accessing memory in-directly. I’m sure ryzen master game mode will be much more important here. In future games (more likely applications) can figure this out via core pinning for various threads, etc. This isn’t a gaming CPU anyway.

But hey, this is something AMD can maybe alleviate in future versions somewhat with more/better/faster on-die cache. Or maybe some nearby / on-die HBM as L4 cache.

We really are at a point where we’re going to have to see real changes in game engines to take proper advantage of these new NUMA CPUs.

Application software will get there first, games are likely good with current CPU power for a long while yet. But eventually, games too will have to adapt.

x399 has 8 memory slots, so it could use channel per memory slot. But shouldn’t we get something like x499 mobos for TR2 launch? They suggested full 128pci-e lanes as epyc 32core equivalent, thus we can assume 8 channel memory too.

@anon46267848

can you provide ref?

if it turns out true for 4channel memory, then it means we again have 2 duds, and amd was able to squeeze 32 cores within 2 stacks like TR1 was. Thus we won’t have the bottleneck with quad channels. (offering 64cores per cpu for epyc line)

not true at all. Did you read what @anon46267848 said?

32 core TR2 is going to have 4 dies of 8 cores each. Two dies are going to have no integrated memory controllers (they’ll be fused off), which means they’ll have to use Infinity Fabric to retrieve data.

i asked for reference, on that. As I cannot find any amd slides stating that.

btw.

Let me see what I can do. The video is in my watched history.

btw, its not that easy to fuse off memory controllers… as they are part of wafer.

i mean how would you fuse off memory controller… they would need to kill it with laser, bios hacks to hide channels, or produce a version without memory controller. Cost inefficient.

I want it to be 8 channel just as much as you do, but around 2:15, Jim Anderson himself says “All four dies are hot.”

If it fits in a X399 board it has no other option than to be quad channel. That’s just how it works.

x399 not necessarily. You could still get use of the memory controllers if they exist per design (which they do). But it very well could be feature for x499 boards, as a selling point.

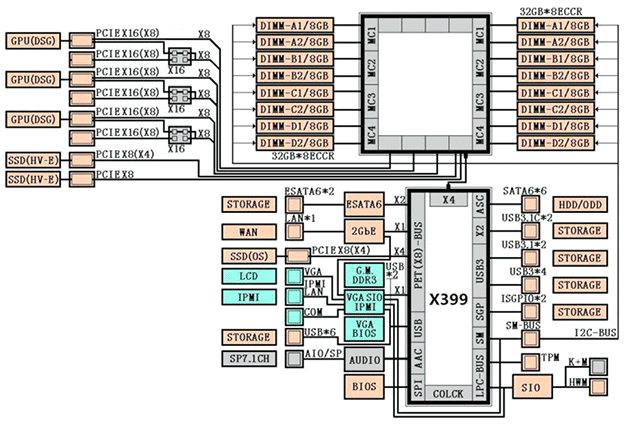

x399 design layout

// still watching to see if he states quad-memory channel. (He never spoke about memory channels.)

https://www.anandtech.com/show/12906/amd-reveals-threadripper-2-up-to-32-cores-250w-x399-refresh

Apparently this was already posted, but it’s equally worth reading.